### EV12DS460AZP

Commercial and Industrial Grade Low power 12-bit 6.0GSps Digital to Analog Converter with 4/2:1 Multiplexer Datasheet DS1167

# **MAIN FEATURES**

- 12-bit resolution

- 6.0 GSps guaranteed conversion rate

- 7.0 GSps operation

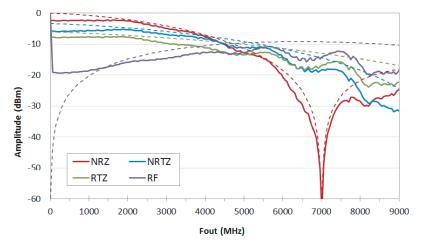

- -3 dB Analog output Bandwidth of 7.5 GHz

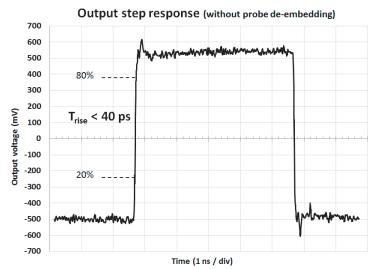

(30 ps rise and fall time on DAC output step response)

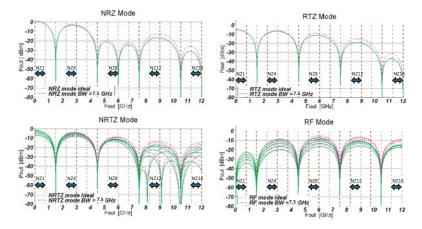

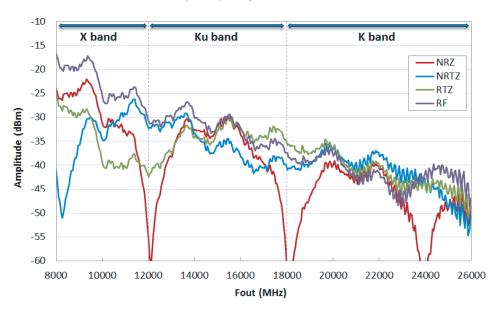

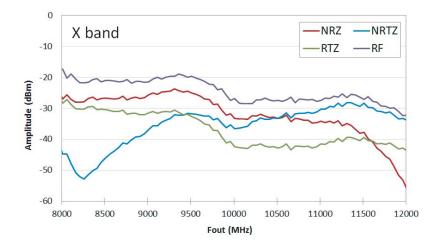

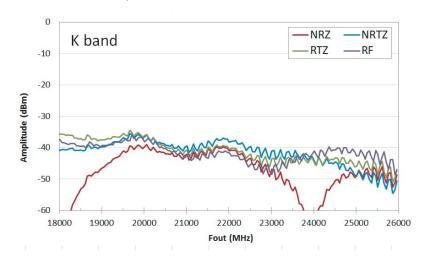

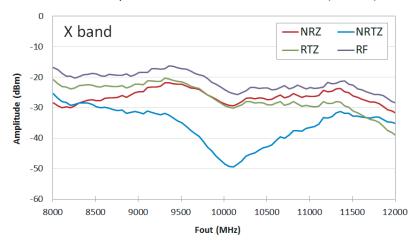

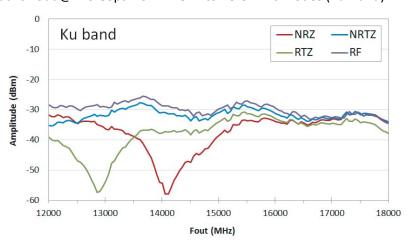

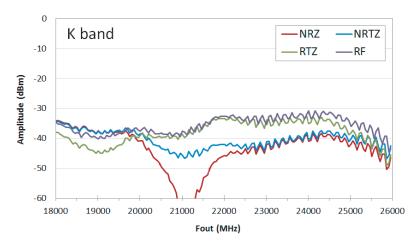

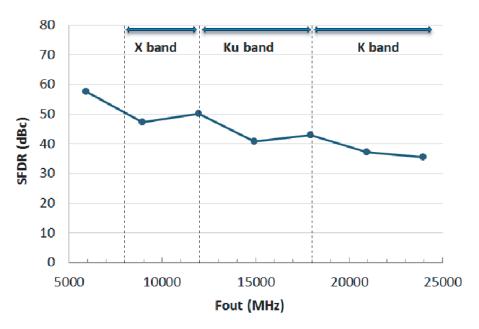

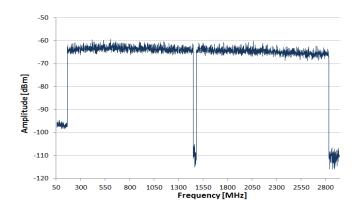

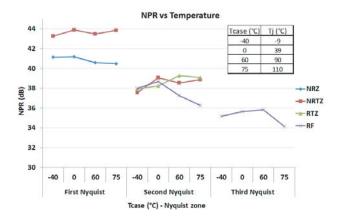

- Support RF signal synthesis up to 12 GHz (X-band)

- Support RF signal synthesis up to 24 GHz (with reduced output power)

- 4:1 or 2:1 integrated parallel MUX (selectable)

- Selectable output modes:

Return To Zero (RTZ), Non Return to Zero (NRZ), Narrow

Return To Zero (NRTZ) and Radio Frequency (RF)

- Low latency time: 3 clock cycles

- 2.6 Watt Power Dissipation (in 4:1 MUX)

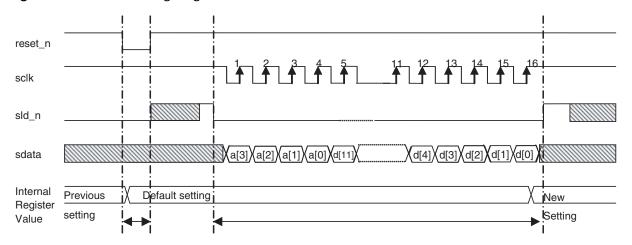

- 3 Wires Serial Interface

- Functions:

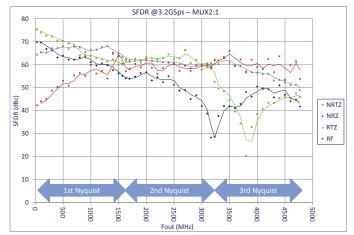

- Selectable MUX ratio 4:1 (up to 6.0 GSps), 2:1 (up to 3.2 GSps)

- User-friendly functions, digitally controlled through a 3WSI serial interface:

- Gain Adjustment

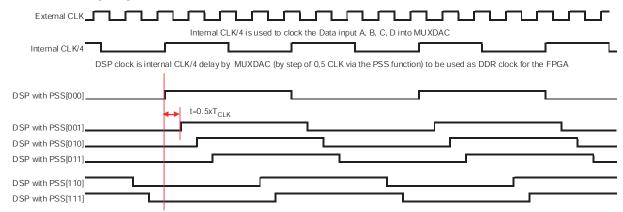

- Output clock division selection (possibility to change the division ratio of the DSP clock) (OCDS)

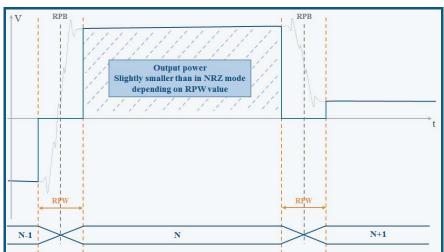

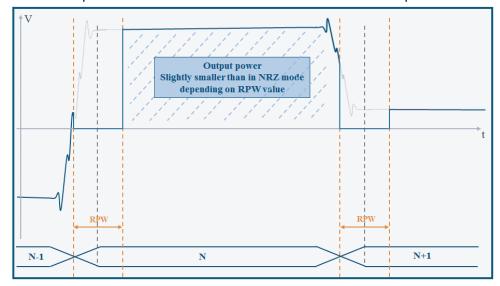

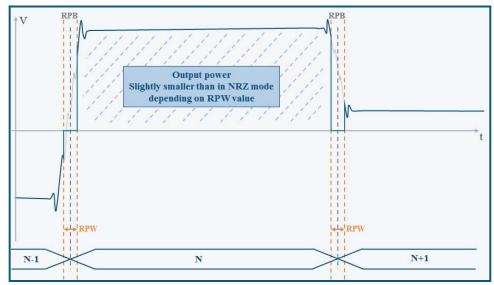

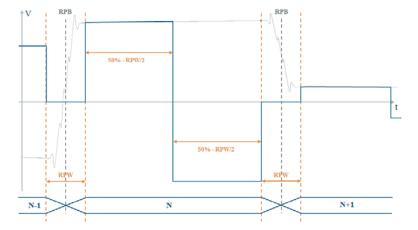

- Reshaped Pulse Width (RPW) and Reshaped Pulse Begin (RPB) adjustments for performance optimization

- Clock phase shift select for synchronization with DSP (PSS[2:0])

- Input Under Clocking Mode by 1/2/4 (IUCM)

- Direct access available for bit OCDS and PSS

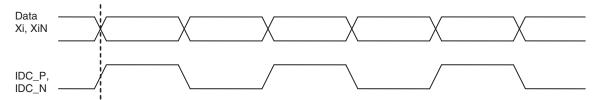

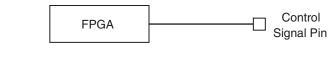

- Input data check bit for timing interface with FPGA check (IDC)

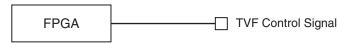

- Timing violation flag (setup or hold) for FPGA

- communication monitoring (TVF)

- LVDS differential data input and DSP clock output.

- Analog output differential swing: 1Vpp (100 $\Omega$  differential impedance)

- External SYNC that can be used for synchronization of multiple DACs

- Power supplies: 3.3 V (Digital), 3.3V & 5V (Analog)

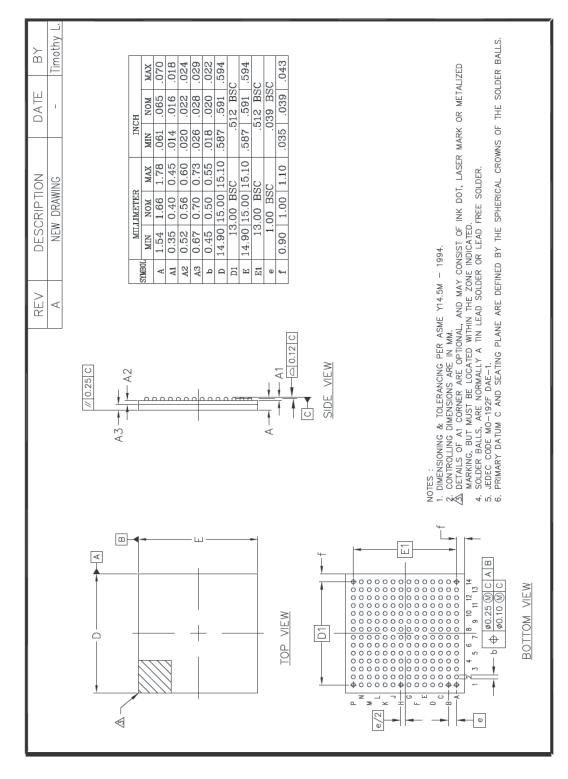

- FpBGA package (15 x 15 mm body size, 1 mm pitch)

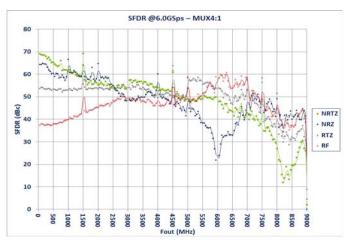

# PERFORMANCES @ 6.0 GSps

- SEDR

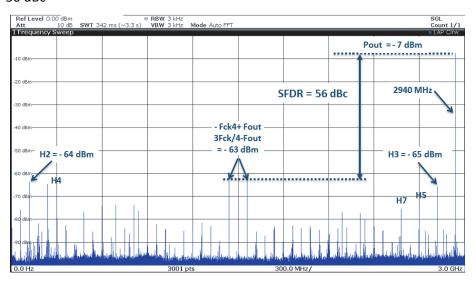

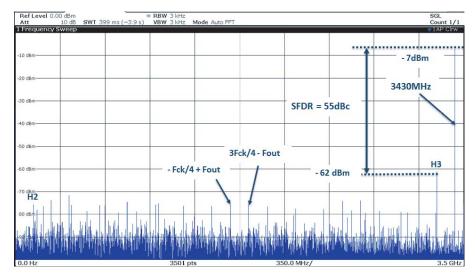

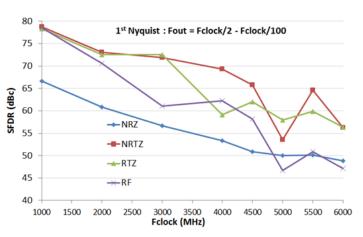

- 1<sup>st</sup> Nyquist (NRTZ 2940 MHz): SFDR = 56 dBc

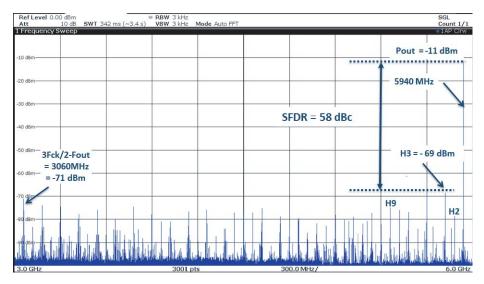

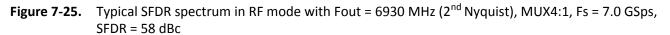

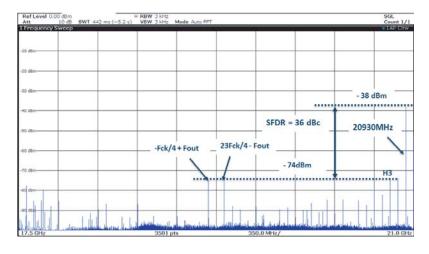

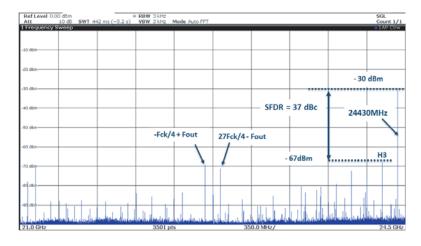

- $-2^{nd}$  Nyquist (RF 5940 MHz): SFDR = 58 dBc

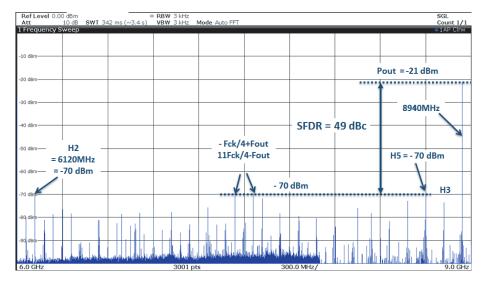

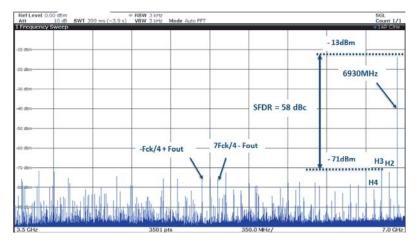

- $-3^{rd}$  Nyquist (RF 8940 MHz): SFDR = 49 dBc

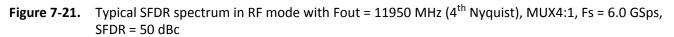

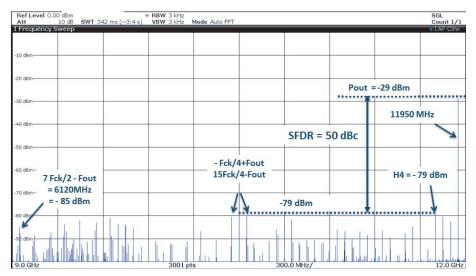

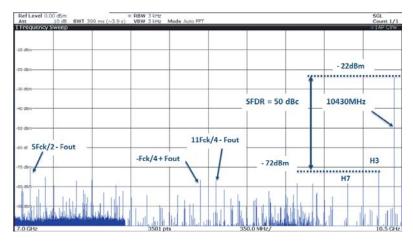

- 4<sup>th</sup> Nyquist (RF 11950 MHz): SFDR = 49 dBc

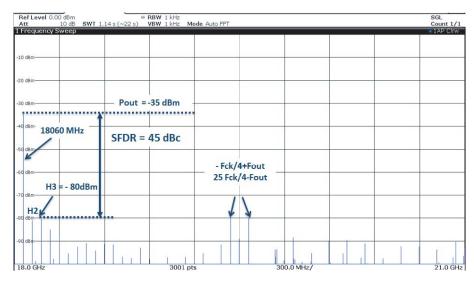

- 7<sup>th</sup> Nyquist (RF 18070 MHz): SFDR = 43 dBc

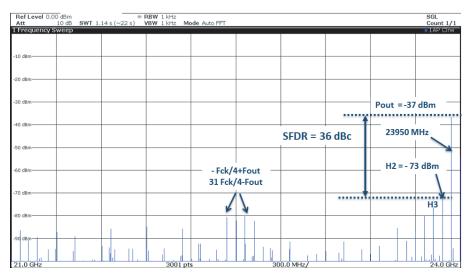

- 8<sup>th</sup> Nyquist (RF 23950 MHz): SFDR = 38 dBc

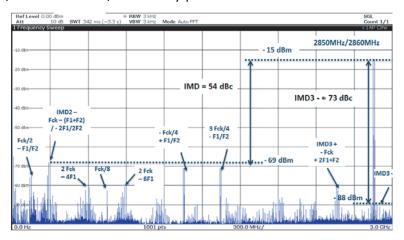

- IMD3 Dual-tone

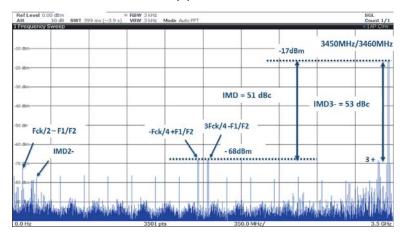

- 1<sup>st</sup> Nyquist (NRTZ 2850 & 2860 MHz): IMD3 = 73 dBc

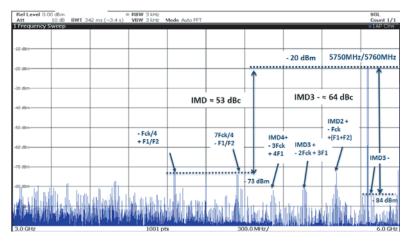

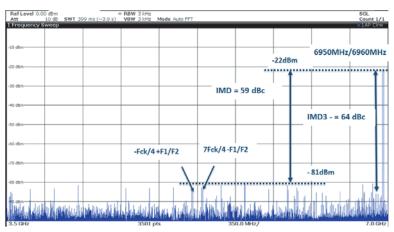

- $-2^{nd}$ Nyquist (RF 5750 & 5760 MHz): IMD3 = 64 dBc

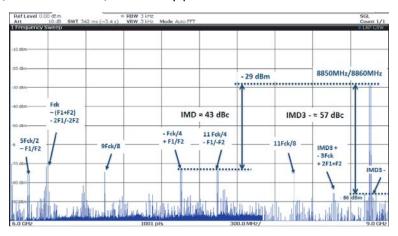

- $-3^{rd}$  Nyquist (RF 8850 & 8860 MHz): IMD3 = 57 dBc

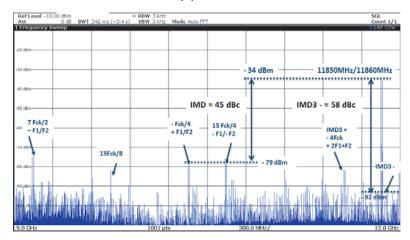

- 4<sup>th</sup> Nyquist (RF 11850 & 11860 MHz): IMD3 = 58 dBc

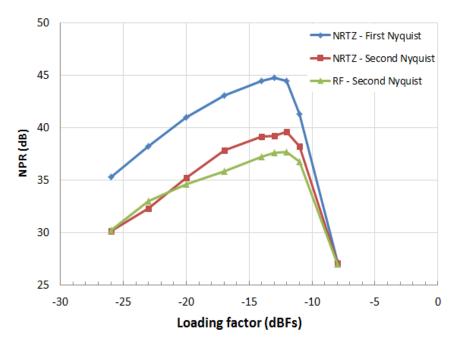

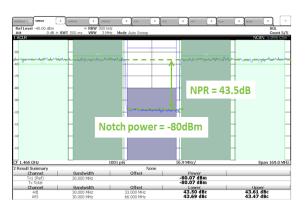

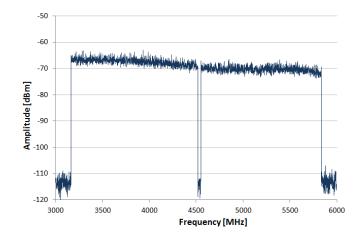

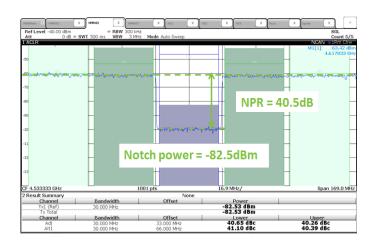

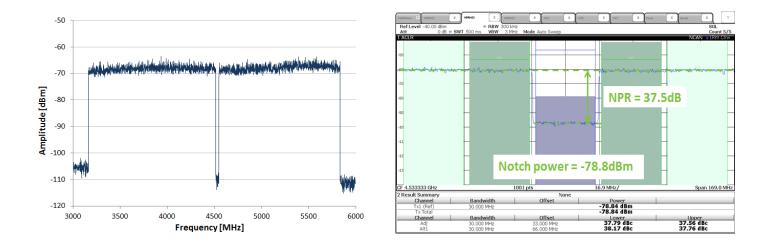

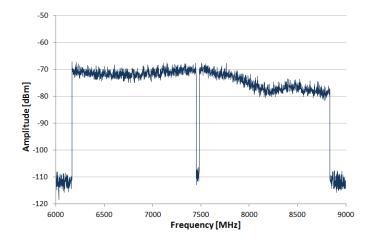

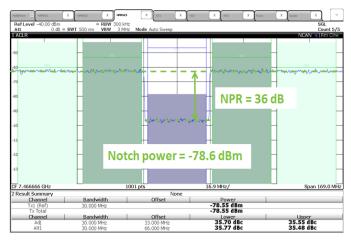

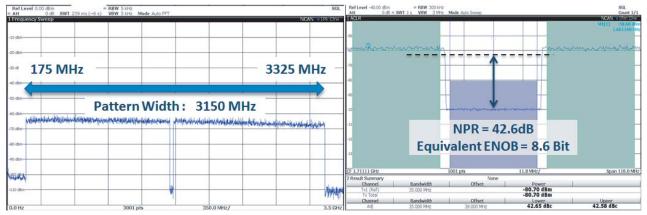

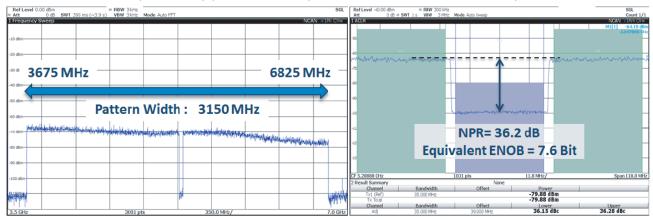

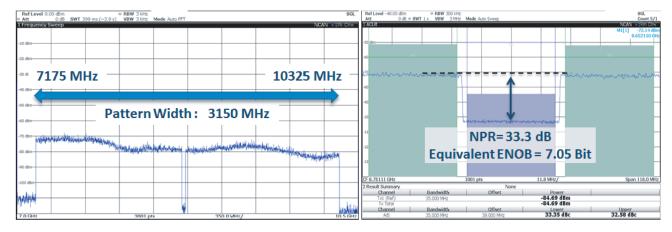

- Broadband NPR at -14 dBFS Loading Factor (90% of full Nyquist zone)

- 1<sup>st</sup> Nyquist (NRTZ): NPR = 44 dB, 8.8 Bit Equivalent

- 2<sup>nd</sup>Nyquist (NRTZ): NPR = 39.5 dB, 8.1 Bit Equivalent

- 3<sup>rd</sup> Nyquist (RF): NPR = 36.5 dB, 7.6 Bit Equivalent

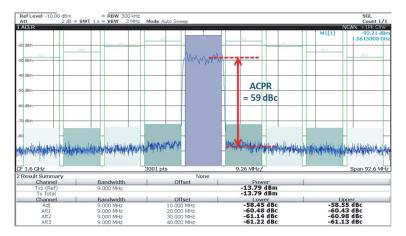

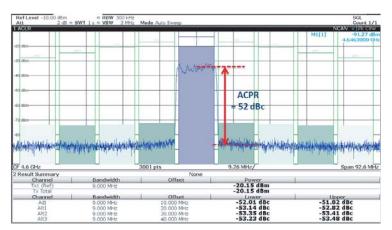

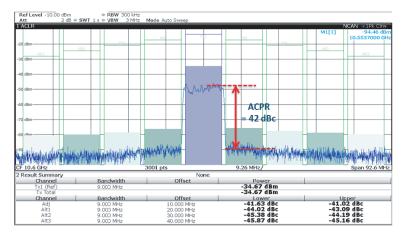

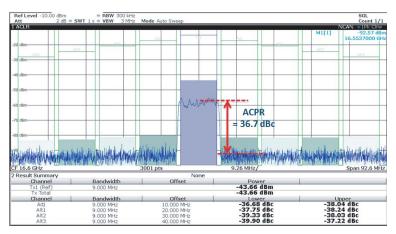

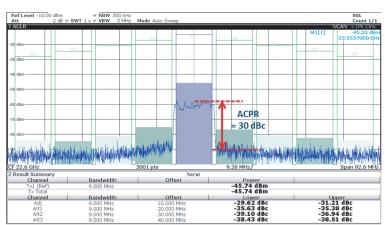

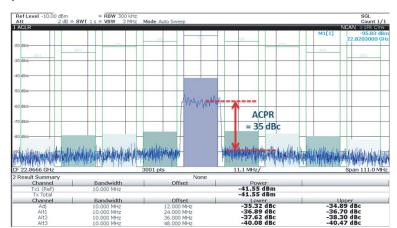

- ACPR = 42 dBc, channel width = 10 MHz QPSK, carrier frequency = 10.6 GHz (X-Band)

- DOCSIS 3.0 Compatible

Whilst Teledyne e2v Semiconductors SAS has taken care to ensure the accuracy of the information contained herein it accepts no responsibility for the consequences of any use thereof and also reserves the right to change the specification of goods without notice. Teledyne e2v Semiconductors SAS accepts no liability beyond the set out in its standard conditions of sale in respect of infringement of third party patents arising from the use of the devices in accordance with information contained herein.

Teledyne e2v Semiconductors SAS, avenue de Rochepleine 38120 Saint-Egrève, France

П

Holding Company: Teledyne e2v Semiconductors SAS

Telephone: +33 (0)4 76 58 30 00

Contact Teledyne e2v by e-mail: hotline-bdc@teledyne-e2v.com or visit www.teledyne-e2v.com for global sales and operations centres

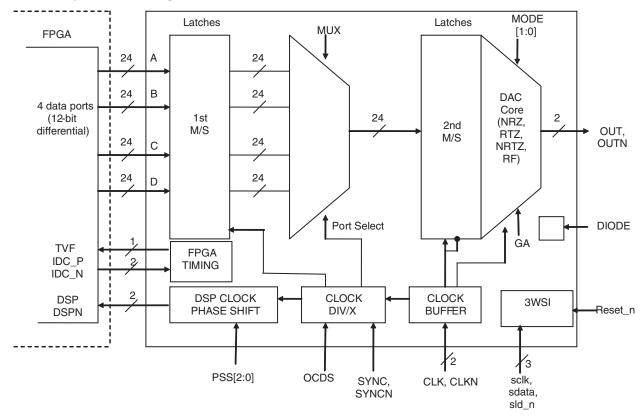

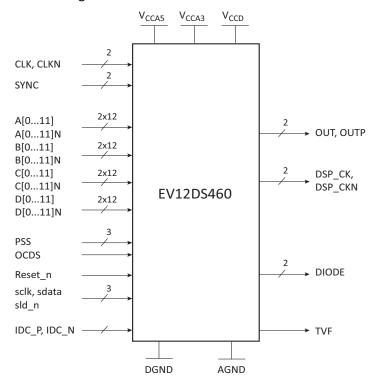

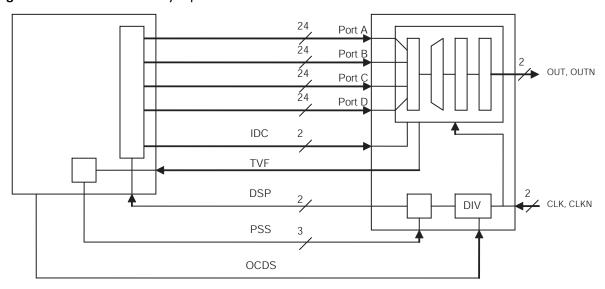

## 1. BLOCK DIAGRAM

Figure 1-1. Simplified block diagram

# 2. DESCRIPTION

The EV12DS460A is a 12-bit 6.0 GSps DAC with an integrated 4:1 or 2:1 multiplexer and 7.5 GHz output bandwidth, allowing easy interface with standard FPGAs thanks to user friendly features such as DSP clock, OCDS, PSS, TVF.

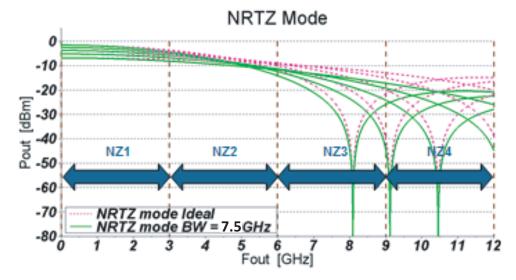

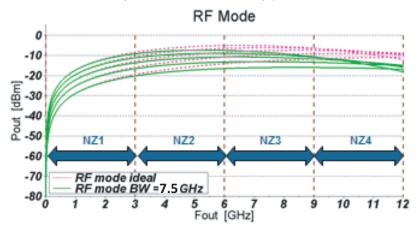

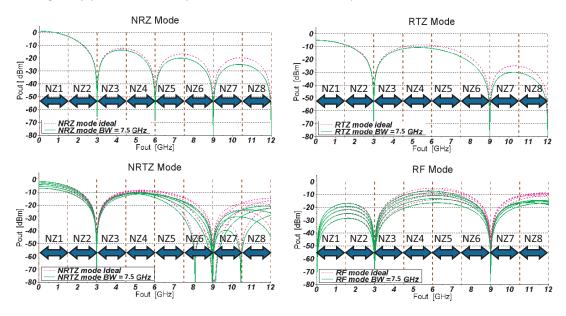

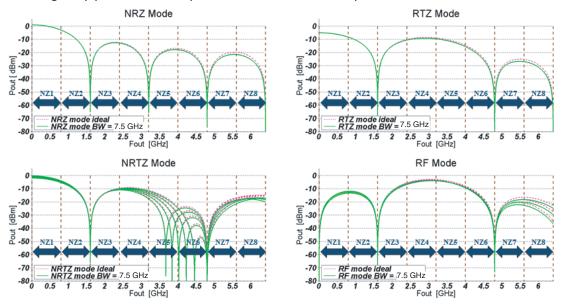

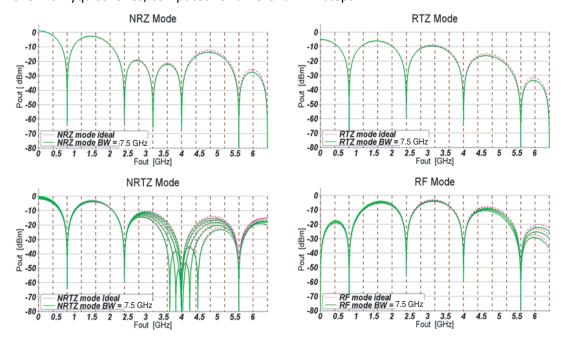

It embeds 4 different output modes (NRZ, RTZ, NRTZ and RF) that allow performance optimizations depending on the Nyquist zone of interest.

# 3. ELECTRICAL CHARACTERISTICS

# 3.1 Absolute Maximum ratings

**Table 3-1.** Absolute maximum ratings

|                                                                 |                                                                                                            | Va   | lue                    | Unit |

|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------|------------------------|------|

| Parameter                                                       | Symbol                                                                                                     | min  | max                    |      |

| V <sub>CCA5</sub> analog supply voltage                         | V <sub>CCA5</sub>                                                                                          | -0.6 | 6.0                    | V    |

| V <sub>CCA3</sub> analog supply voltage                         | V <sub>CCA3</sub>                                                                                          | -0.6 | 4.0                    | V    |

| V <sub>CCD</sub> digital supply voltage                         | V <sub>CCD</sub>                                                                                           | -0.6 | 4.0                    | V    |

| Digital input (on each single-ended input), IDC and SYNC signal | [P <sub>0</sub> P <sub>11</sub> ],<br>[P <sub>0N</sub> P <sub>11N</sub> ],<br>IDC_P, IDC_N,<br>SYNC, SYNCN | 0    | V <sub>CCA3</sub>      | V    |

| Digital input maximum differential swing<br>Port P = A, B, C, D |                                                                                                            |      | 2.0                    | Vpp  |

| Master clock input (on each single ended input)                 | CLK, CLKN                                                                                                  | 1.0  | 4.0                    | V    |

| Master clock maximum differential swing                         |                                                                                                            |      | 3                      | Vpp  |

| Control function inputs voltage                                 | PSS[02], OCDS,<br>reset_n, sclk,<br>sdata, sld_n                                                           | -0.4 | V <sub>CCD</sub> + 0.4 | V    |

| Junction temperature                                            | T <sub>J</sub>                                                                                             |      | 170                    | °C   |

| Parameter                                | Symbol  | Value                                        | Unit |

|------------------------------------------|---------|----------------------------------------------|------|

| Electrostatic discharge human body model | ESD HBM | JESD22-A114-E Class 1C<br>(1000V to < 2000V) |      |

| Electrostatic discharge machine model    | ESD MM  | JESD22-A115-C Class M2<br>(100V to < 200V)   | V    |

| Latch up                                 |         | JEDEC 78B<br>Class I & Class II              |      |

| Moisture sensitivity level               | MSL     | 3                                            |      |

| Storage temperature range                | Tstg    | -65 to +150                                  | °C   |

Notes:

- 1. Absolute maximum ratings are limiting values (referenced to GND = 0V), to be applied individually, while other parameters are within specified operating conditions. Long exposure to maximum rating may affect device reliability.

- 2. All integrated circuits have to be handled with appropriate care to avoid damages due to ESD. Damage caused by inappropriate handling or storage could range from performances degradation to complete failure.

- 3. Maximum ratings enable active inputs with DAC powered off.

- 4. Maximum ratings enable floating inputs with DAC powered on.

- 5. DSP clock and TVF output buffers must not be shorted to ground or positive power supply.

### 3.2 Recommended conditions of use

**Table 3-2.** Recommended conditions of use

| Parameter                                                                                                                                      | Symbol                                                                                                     | Recommended<br>Value  | Unit          | Note   |

|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------|---------------|--------|

| V <sub>CCA5</sub> analog supply voltage                                                                                                        | V <sub>CCA5</sub>                                                                                          | 5.0                   | V             | (1)(2) |

| V <sub>CCA3</sub> analog supply voltage                                                                                                        | V <sub>CCA3</sub>                                                                                          | 3.3                   | V             | (1)(2) |

| V <sub>CCD</sub> digital supply voltage                                                                                                        | V <sub>CCD</sub>                                                                                           | 3.3                   | V             | (1)(2) |

| Digital input (on each single ended input), IDC and SYNC signal Port P = A, B, C, D $V_{\rm IL}$ $V_{\rm IH}$ Digital input differential swing | [P <sub>0</sub> P <sub>11</sub> ],<br>[P <sub>0N</sub> P1 <sub>1N</sub> ],<br>IDC_P, IDC_N,<br>SYNC, SYNCN | 1.075<br>1.425<br>350 | V<br>V<br>mVp |        |

| Master Clock input differential mode swing                                                                                                     | CLK, CLKN                                                                                                  | 1.4                   | Vpp           |        |

| Master Clock input power level (differential mode)                                                                                             | P <sub>CLK</sub>                                                                                           | 4                     | dBm           | (3)    |

| Control function inputs $V_{IL} \\ V_{IH}$                                                                                                     | PSS[02], OCDS,<br>reset_n,<br>sclk, sdata, sld_n                                                           | 0<br>V <sub>CCD</sub> | V<br>V        |        |

| RPB & RPW settings for enhanced dynamic performance 6.0 GSps in NRTZ mode                                                                      | RPB<br>RPW                                                                                                 | RPB2<br>RPW0          | _<br>_        | (4)    |

| RPB & RPW settings for enhanced dynamic performance 6.0 GSps in RF mode                                                                        | RPB<br>RPW                                                                                                 | RPB1<br>RPW0          | -<br>-        | (4)    |

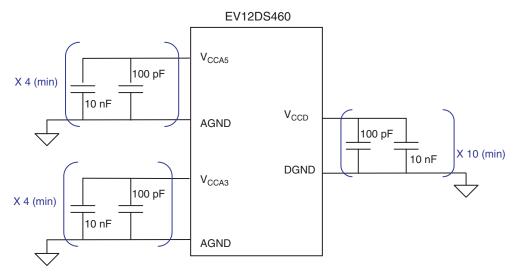

Notes: 1. See Section 8.8 on page 83 for power on requirement

- 2. No power-down sequencing is required

- 3. Clock input power can be decreased when clock frequency is lower as long as it respects the specification.

- 4. A good compromise for RPB & RPW values is defined for a 6.0 GHz clock frequency. This couple of values depends on the clock frequency. These recommended RPB/RPW couples have been chosen to offer good performances over the Nyquist of use (1<sup>st</sup> and 2<sup>nd</sup> in NRTZ mode, 2<sup>nd</sup> and 3<sup>rd</sup> in RF mode) at Fclock = 6.0 GHz. For specific condition (for example looking at the SFDR at a particular output frequency), a RPB/RPW optimization can increase performances.

# 3.3 DC Electrical Characteristics

Unless otherwise specified:  $V_{CCA5} = 5V$ ,  $V_{CCA3} = 3.3V$ ,  $V_{CCD} = 3.3V$ , 4:1 MUX ratio, room temperature, typical swing on input data, typical Pclk, master clock input jitter is below 100 fs rms integrated over 11 GHz bandwidth.

**Table 3-3.** DC Electrical characteristics

| Parameter                                                         | Symbol            | Min   | Тур   | Max   | Unit | Notes | Test<br>level <sup>(1)</sup> |

|-------------------------------------------------------------------|-------------------|-------|-------|-------|------|-------|------------------------------|

| RESOLUTION                                                        |                   |       | 12    |       | bit  |       |                              |

| POWER REQUIREMENTS                                                |                   |       |       |       | -    | *     |                              |

| Power Supply voltage                                              |                   |       |       |       |      |       |                              |

| - Analog                                                          | $V_{CCA5}$        | 4.75  | 5     | 5.25  | V    | (2)   | 1                            |

| - Analog                                                          | V <sub>CCA3</sub> | 3.15  | 3.3   | 3.45  | V    |       | _                            |

| - Digital                                                         | $V_{CCD}$         | 3.15  | 3.3   | 3.45  | V    |       |                              |

| Power Supply current (4:1 MUX)                                    |                   |       |       |       |      |       |                              |

| - Analog                                                          | I <sub>CCA5</sub> | 85    | 100   | 115   | mA   | (8)   | 1                            |

| - Analog                                                          | I <sub>CCA3</sub> | 170   | 205   | 240   | mA   |       | _                            |

| - Digital                                                         | I <sub>CCD</sub>  | 360   | 425   | 490   | mA   |       |                              |

| Power Supply current (2:1 MUX)                                    |                   |       |       |       |      |       |                              |

| - Analog                                                          | I <sub>CCA5</sub> | 85    | 100   | 115   | mA   | (8)   | 1                            |

| - Analog                                                          | I <sub>CCA3</sub> | 170   | 205   | 240   | mA   |       | -                            |

| - Digital                                                         | I <sub>CCD</sub>  | 310   | 370   | 430   | mA   |       |                              |

| Power dissipation (4:1 MUX)                                       | PD4               | 2.2   | 2.6   | 3     | W    | (8)   | 1                            |

| Power dissipation (2:1 MUX)                                       | PD2               | 2     | 2.4   | 2.8   | W    | (8)   | 1                            |

| DIGITAL DATA INPUTS, SYNC and IDC INPUTS                          |                   |       |       |       |      |       |                              |

| Logic compatibility                                               |                   |       | LVDS  | _     |      |       |                              |

| Digital input voltages:                                           |                   |       |       |       |      |       |                              |

| - Differential input voltage                                      | VID               | 100   | 350   | 500   | mVp  |       | 1                            |

| - Common mode                                                     | VICM              | 1     | 1.25  | 1.6   | V    |       | 1                            |

| Input capacitance from each single input to ground                |                   |       |       | 2     | pF   |       | 5                            |

| Differential input resistance                                     |                   | 80    | 100   | 120   | Ω    |       | 1                            |

| CLOCK INPUTS                                                      |                   |       |       |       |      |       |                              |

| Input voltages (Differential operation swing)                     |                   | 0.6   | 1.4   | 2.4   | Vpp  |       | 1                            |

| Power level (Differential operation)                              |                   | -4    | 4     | +8.5  | dBm  | (3)   | 1                            |

| Common mode                                                       |                   | 2.4   | 2.5   | 2.6   | V    |       | 1                            |

| Input capacitance from each single input to ground (at die level) |                   |       |       | 2     | pF   |       | 5                            |

| Differential Input resistance:                                    |                   | 80    | 100   | 120   | Ω    |       | 1                            |

| DSP CLOCK OUTPUT                                                  |                   |       |       |       |      | •     |                              |

| Logic compatibility                                               |                   |       | LVDS  |       |      |       |                              |

| Output voltages:                                                  |                   |       |       |       |      |       |                              |

| - Differential output voltage                                     | VOD               | 240   | 350   | 450   | mVp  | (10)  | 1                            |

| - Common mode                                                     | VOCM              | 1.125 | 1.250 | 1.375 | v .  |       | 1                            |

# EV12DS460AZP

Table 3-3.

DC Electrical characteristics (Continued)

| Parameter                                                                             | Symbol     | Min                     | Тур                     | Max                     | Unit     | Notes | Test<br>level <sup>(1)</sup> |

|---------------------------------------------------------------------------------------|------------|-------------------------|-------------------------|-------------------------|----------|-------|------------------------------|

| ANALOG OUTPUT                                                                         |            |                         |                         |                         |          |       |                              |

| Full-scale Differential output voltage (100 $\!\Omega$ differentially terminated)     |            | 0.92                    | 1                       | 1.08                    | Vpp      |       | 1                            |

| Full-scale output power (differential output on 100 $\Omega$ )                        |            |                         | +1                      |                         | dBm      | (4)   | 1                            |

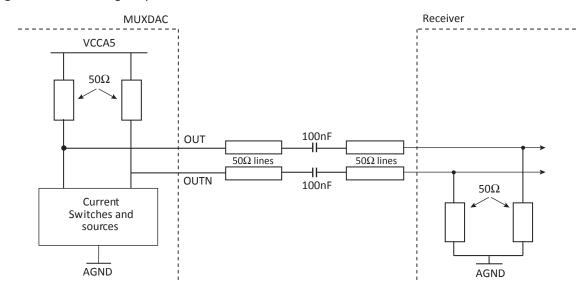

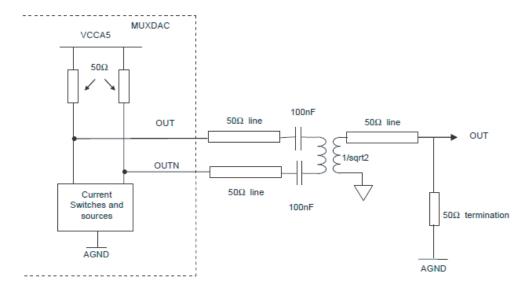

| Single-ended mid-scale output voltage (50 $\!\Omega$ terminated)                      |            | V <sub>CCA5</sub> -0.50 | V <sub>CCA5</sub> -0.43 | V <sub>CCA5</sub> -0.36 | ٧        | (5)   | 1                            |

| Output capacitance                                                                    |            |                         | 1.5                     |                         | pF       |       | 5                            |

| Nominal Output internal differential resistance                                       |            | 90                      | 100                     | 110                     | Ω        |       | 1                            |

| Output VSWR (using Teledyne e2v's evaluation board)<br>2.25 GHz<br>4.5 GHz<br>6.0 GHz |            |                         | 1.2<br>1.4<br>1.7       |                         |          |       | 4                            |

| –3 dB Analog Output bandwidth                                                         |            |                         | 7.5                     |                         | GHz      |       | 4                            |

| FUNCTIONS                                                                             |            |                         |                         |                         |          |       |                              |

| Digital functions: sdata, sld_n, sclk, reset_n, OCDS, PSS - Logic 0 - Logic 1         | VIL<br>VIH | 1.6                     | 0<br>V <sub>CCD</sub>   | 0.8                     | V<br>V   |       | 1                            |

| sdata, sld_n, sclk, reset_n - Low Level input current - High Level input current      | IIL<br>IIH | -120<br>10              | -55<br>80               | -10<br>120              | μA<br>μA |       | 1                            |

| OCDS, PSS: - Low Level input current - High Level input current                       | IIL<br>IIH | -150<br>50              | -100<br>100             | -50<br>150              | μA<br>μA |       | 1                            |

| Digital output function TVF - Logic 0                                                 | VOL<br>VOH | 2.3                     |                         | 0.6                     | V<br>V   | (8)   | 1                            |

| - Logic 1                                                                             | IOL<br>IOH |                         |                         | 500<br>500              | μA<br>μA |       | 5                            |

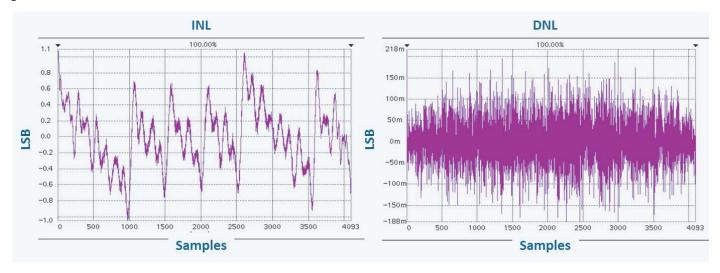

| DC ACCURACY                                                                           |            |                         |                         |                         |          |       |                              |

| Differential Non-Linearity                                                            | DNL+       |                         | 0.4                     | 0.8                     | LSB      |       | 1                            |

| Differential Non-Linearity                                                            | DNL-       | -0.8                    | -0.4                    |                         | LSB      |       | 1                            |

| Integral Non-Linearity                                                                | INL+       |                         | 0.7                     | 2.5                     | LSB      |       | 1                            |

| Integral Non-Linearity                                                                | INL-       | -2.5                    | -0.7                    |                         | LSB      |       | 1                            |

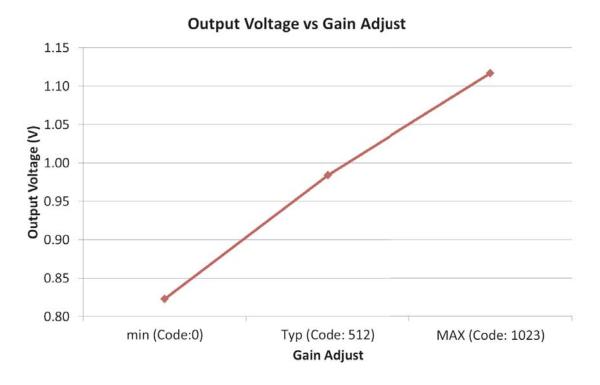

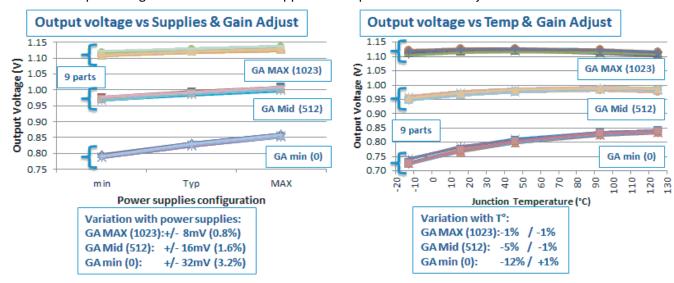

| DC GAIN                                                                               |            |                         |                         |                         |          |       | ,                            |

| DAC output voltage (@ default value)                                                  |            | 0.92                    |                         | 1.08                    | Vpp      | (6)   | 1                            |

| DAC output voltage adjustment step                                                    |            | -5                      | 0.3                     | +5                      | mV       |       | 1                            |

| DAC output voltage after optimum 3WSI adjustment                                      |            | 0.995                   | 1                       | 1.005                   | Vpp      | (6)   | 1                            |

| DAC output voltage sensitivity to supplies                                            |            |                         | 3.2                     | 5                       | %        | (7)   | 1                            |

| DAC output voltage drift over temperature                                             |            |                         | 45                      | 55                      | mVpp     | (9)   | 4                            |

Notes: 1. See Section 3.6 on page 18 for explanation of test levels.

- 2. See Section 8.8 on page 83 for power up sequencing.

- 3. For use in higher Nyquist zone, it is recommended to use higher power clock within the limit.

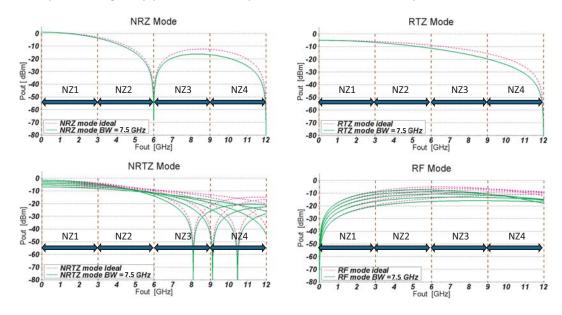

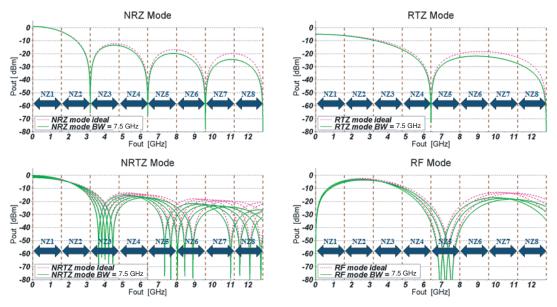

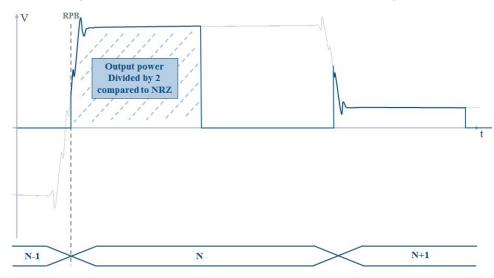

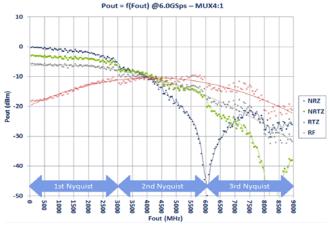

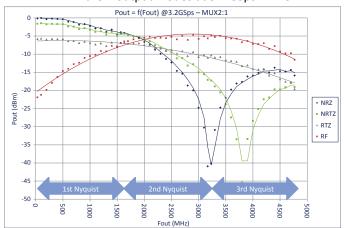

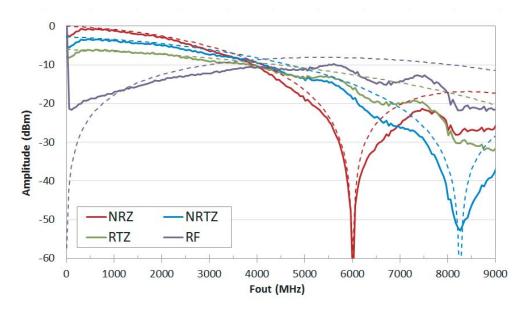

- 4. In NRZ mode only. For the other reshaped modes, the output power will be lower by construction. See Figure 5-2 and Figure 5-3.

- 5. These values are mainly for information as single-ended operation in not recommended.

- 6. The DAC output voltage can be adjusted close to 1Vpp thanks to the GAIN control register in the 3WSI.

- 7. DAC output voltage sensitivity to supplies = DAC output voltage at Vmax DAC output at Vmin. Measurement done with DAC Gain Adjust at its default value (3WSI GA register default value = 0x200)

Min and Max values are given versus supplies at room temperature

- 8. Tested with IOL & IOH =  $500\mu$ A

- 9. DAC output voltage sensitivity to temperature = DAC output voltage at Tmax DAC output voltage at Tmin. Measurement done with DAC Gain Adjust at its default value (3WSI GA register default value = 0x200) Min and Max values are given versus temperature with typical supplies

- 10. It has been noted that at extreme low temperature and/or V<sub>CCD</sub> min, the swing of the DSP clock signal is reduced. However it stays above the 100mVp generally specified for LVDS input swing and thus should not be an issue at the system level.

#### 3.4 AC Electrical Characteristics

Unless otherwise specified:  $V_{CCA5} = 5V$ ,  $V_{CCA3} = 3.3V$ ,  $V_{CCD} = 3.3V$ , 4:1 MUX ratio, room temperature, typical swing on input data, typical Pclk, master clock input jitter is below 100 fs rms integrated over 11 GHz bandwidth.

## Important note on expected performances:

Figures for performances in NRTZ and RF modes are given for recommended value of RPW (Reshaping Pulse Width). Tuning of RPW by customer is recommended. Increasing RPW improves linearity (SFDR) at the expense of carrier output power (SNR). Decreasing RPW improves carrier output power (SNR) at the expense of linearity (SFDR).

Figures for performance in RTZ, NRTZ and RF modes are given for recommended value of RPB (Reshaping Pulse Begin) which are digitally programmable through the 3 Wires Serial Interface (3WSI).

Values between brackets are given for optimum RPB/RPW values. Optimum settings may differ from part to part.

See Section 5.3 on page 27 for more information on RPW and RPB settings. Recommended values for RPB and RPW are given in Table 3-2.

# EV12DS460AZP

Table 3-4.

AC Electrical Characteristics NRZ Mode (First Nyquist Zone)

| Parameter                                            | Symbol | Min | Тур         | Max | Unit   | Notes   | Test<br>level <sup>(1)</sup> |

|------------------------------------------------------|--------|-----|-------------|-----|--------|---------|------------------------------|

| Single-tone Spurious Free Dynamic Range              | 1      |     |             |     |        |         |                              |

| 4:1 MUX                                              |        |     |             |     |        |         |                              |

| Fs = 6.0 GSps @ Fout = 60 MHz 0 dBFS                 |        |     | 66          |     |        |         | 4                            |

| Fs = 6.0 GSps @ Fout = 2940 MHz 0 dBFS               | SFDR   |     | 49          |     | dBc    | (2) (3) | 4                            |

| Fs = 3.0 GSps @ Fout = 30 MHz 0 dBFS                 |        | 64  | 71          |     |        |         | 1                            |

| Fs = 3.0 GSps @ Fout = 1470 MHz 0 dBFS               |        | 51  | 58          |     |        |         | 1                            |

| 2:1 MUX                                              |        |     |             |     |        |         |                              |

| Fs = 3.2 GSps @ Fout = 32 MHz 0 dBFS                 |        |     | 70          |     |        |         | 4                            |

| Fs = 3.2 GSps @ Fout = 1568 MHz 0 dBFS               | SFDR   |     | 55          |     | dBc    | (2) (3) | 4                            |

| Fs = 1.5 GSps @ Fout = 15 MHz 0 dBFS                 |        | 65  | 75          |     |        |         | 1                            |

| Fs = 1.5 GSps @ Fout = 735 MHz 0 dBFS                |        | 57  | 64          |     |        |         | 1                            |

| Highest spur level                                   | ,      |     |             |     |        |         |                              |

| 4:1 MUX                                              |        |     |             |     |        |         |                              |

| Fs = 6.0 GSps @ Fout = 60 MHz 0 dBFS                 |        |     | <b>-</b> 65 |     |        |         | 4                            |

| Fs = 6.0 GSps @ Fout = 2940 MHz 0 dBFS               |        |     | -54         |     |        |         | 4                            |

| Fs = 3.0 GSps @ Fout = 30 MHz 0 dBFS                 |        |     | -70         |     | dBm    |         | 1                            |

| Fs = 3.0 GSps @ Fout = 1470 MHz 0 dBFS               |        |     | -61         |     |        |         | 1                            |

| 2:1 MUX                                              |        |     |             |     |        |         |                              |

| Fs = 3.2 GSps @ Fout = 32 MHz 0 dBFS                 |        |     | <b>-70</b>  |     |        |         | 4                            |

| Fs = 3.2 GSps @ Fout = 1568 MHz 0 dBFS               |        |     | -60         |     | dBm    |         | 4                            |

| Fs = 1.5 GSps @ Fout = 15 MHz 0 dBFS                 |        |     | -74         |     |        |         | 1                            |

| Fs = 1.5 GSps @ Fout = 735 MHz 0 dBFS                |        |     | -66         |     |        |         | 1                            |

| Signal independent Spur (clock-related spur) with 4  | :1 MUX |     |             |     |        |         |                              |

| Fc/2 @ 6.0 GSps                                      |        |     | -80         |     | dBm    |         | 4                            |

| Fc/4 @ 6.0 GSps                                      |        |     | -75         |     | dBm    |         | 4                            |

| Self-Noise Density at code 0 or 4095 @ 6.0 GSps      |        |     | <-160       |     | dBm/Hz |         | 4                            |

| Noise Power Ratio                                    |        |     |             |     |        |         |                              |

| −14 dBFS peak to rms loading factor                  |        |     |             |     |        | (4) (=) |                              |

| Fs = 6.0 GSps                                        | NPR    |     | 41.5        |     | dB     | (4) (5) | 4                            |

| 2.667 GHz broadband pattern,<br>33.3 MHz notch width |        |     |             |     |        |         |                              |

| Equivalent ENOB (Computed from NPR figure)           | ENOB   |     | 8.4         |     | Bit    |         | 4                            |

| Signal to Noise Ratio (Computed from NPR figure)     | SNR    |     | 52.5        |     | dB     |         | 4                            |

Table 3-4.

AC Electrical Characteristics NRZ Mode (First Nyquist Zone) (Continued)

| Parameter                                                                                                           | Symbol | Min | Тур | Max | Unit | Notes | Test<br>level <sup>(1)</sup> |

|---------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|------|-------|------------------------------|

| Noise Power Ratio  -14 dBFS peak to rms loading factor  Fs = 3 GSps  1.33 GHz broadband pattern, 17 MHz notch width | NPR    | 43  | 46  |     | dB   |       | 1                            |

| Equivalent ENOB (Computed from NPR figure)                                                                          | ENOB   | 8.7 | 9.2 |     | Bit  |       | 1                            |

| Signal to Noise Ratio (Computed from NPR figure)                                                                    | SNR    | 54  | 57  |     | dB   |       | 1                            |

Note:

- 1. See Section 3.6 on page 18 for explanation of test levels.

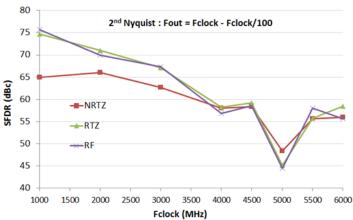

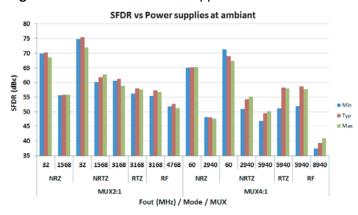

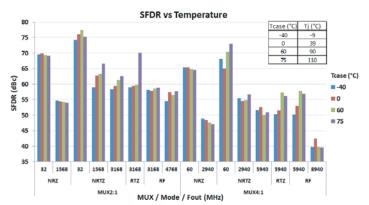

- 2. Refer to Figure 7-40 for SFDR variation versus temperature.

- 3. Refer to Figure 7-39 for SFDR variation versus supplies.

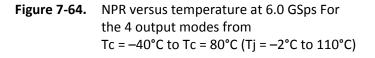

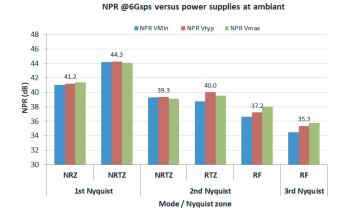

- 4. Refer to Figure 7-64 for NPR variation versus temperature.

- 5. Refer to Figure 7-63 for NPR variation versus supplies.

Table 3-5.

AC Electrical Characteristics NRTZ Mode (First & Second Nyquist Zone)

| Parameter                               | Symbol | Min | Тур     | Max | Unit | Notes   | Test<br>level <sup>(1)</sup> |

|-----------------------------------------|--------|-----|---------|-----|------|---------|------------------------------|

| Single-tone Spurious Free Dynamic Range |        |     |         |     |      |         |                              |

| 4:1 MUX                                 |        |     |         |     |      |         |                              |

| Fs = 6.0 GSps @ Fout = 60 MHz 0 dBFS    |        |     | 69 (69) |     |      |         | 4                            |

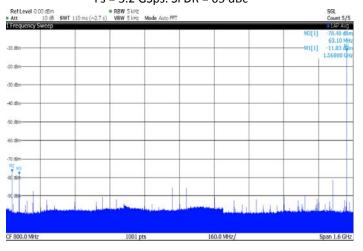

| Fs = 6.0 GSps @ Fout = 2940 MHz 0 dBFS  |        |     | 55 (56) |     |      |         | 4                            |

| Fs = 6.0 GSps @ Fout = 5940 MHz 0 dBFS  | SFDR   |     | 51 (59) |     | dBc  | (2) (3) | 4                            |

| Fs = 3.0 GSps @ Fout = 30 MHz 0 dBFS    |        | 62  | 75      |     |      |         | 1                            |

| Fs = 3.0 GSps @ Fout = 1470 MHz 0 dBFS  |        | 60  | 65      |     |      |         | 1                            |

| Fs = 3.0 GSps @ Fout = 2970 MHz 0 dBFS  |        | 55  | 60      |     |      |         | 1                            |

| 2:1 MUX                                 |        |     |         |     |      |         |                              |

| Fs = 3.2 GSps @ Fout = 32 MHz 0 dBFS    |        |     | 76      |     |      |         | 4                            |

| Fs = 3.2 GSps @ Fout = 1568 MHz 0 dBFS  |        |     | 63      |     |      |         | 4                            |

| Fs = 3.2 GSps @ Fout = 3168 MHz 0 dBFS  | SFDR   |     | 62      |     | dBc  | (2) (3) | 4                            |

| Fs = 1.5 GSps @ Fout = 15 MHz 0 dBFS    |        | 65  | 77      |     |      |         | 1                            |

| Fs = 1.5 GSps @ Fout = 735 MHz 0 dBFS   |        | 63  | 73      |     |      |         | 1                            |

| Fs = 1.5 GSps @ Fout = 1485 MHz 0 dBFS  |        | 51  | 57      |     |      |         | 1                            |

# EV12DS460AZP

Table 3-5.

AC Electrical Characteristics NRTZ Mode (First & Second Nyquist Zone) (Continued)

|                                                       |          |     |                        |     |        |         | Test                 |

|-------------------------------------------------------|----------|-----|------------------------|-----|--------|---------|----------------------|

| Parameter                                             | Symbol   | Min | Тур                    | Max | Unit   | Notes   | level <sup>(1)</sup> |

| Highest spur level (Single tone)                      |          |     |                        |     |        |         |                      |

| 4:1 MUX                                               |          |     |                        |     |        |         |                      |

| Fs = 6.0 GSps @ Fout = 60 MHz 0 dBFS                  |          |     | -72 (-72)              |     |        |         | 4                    |

| Fs = 6.0 GSps @ Fout = 2940 MHz 0 dBFS                |          |     | -62 (-63)              |     |        |         | 4                    |

| Fs = 6.0 GSps @ Fout = 5940 MHz 0 dBFS                |          |     | -66 ( <del>-</del> 75) |     | dBm    |         | 4                    |

| Fs = 3.0 GSps @ Fout = 30 MHz 0 dBFS                  |          |     | -76                    |     |        |         | 1                    |

| Fs = 3.0 GSps @ Fout = 1470 MHz 0 dBFS                |          |     | -69                    |     |        |         | 1                    |

| Fs = 3.0 GSps @ Fout = 2970 MHz 0 dBFS                |          |     | <b>-</b> 76            |     |        |         | 1                    |

| 2:1 MUX                                               |          |     |                        |     |        |         |                      |

| Fs = 3.2 GSps @ Fout = 32 MHz 0 dBFS                  |          |     | <b>-77</b>             |     |        |         | 4                    |

| Fs = 3.2 GSps @ Fout = 1568 MHz 0 dBFS                |          |     | <del>-</del> 67        |     |        |         | 4                    |

| Fs = 3.2 GSps @ Fout = 3168 MHz 0 dBFS                |          |     | -80                    |     | dBm    |         | 4                    |

| Fs = 1.5 GSps @ Fout = 15 MHz 0 dBFS                  |          |     | <b>-</b> 76            |     |        |         | 1                    |

| Fs = 1.5 GSps @ Fout = 735 MHz 0 dBFS                 |          |     | <b>-</b> 76            |     |        |         | 1                    |

| Fs = 1.5 GSps @ Fout = 1485 MHz 0 dBFS                |          |     | -78                    |     |        |         | 1                    |

| Dual-tone over Full Nyquist                           |          |     |                        |     |        |         |                      |

| 4:1 MUX                                               |          |     |                        |     |        |         |                      |

| Fs = 6.0 GSps @ Fout1 = 2850 MHz,                     | IMD      |     | (54)                   |     | dBc    |         | 4                    |

| Fout2 = 2860 MHz -8 dBFS each tone                    | IMD3     |     | (73)                   |     | dBc    |         | 4                    |

| Highest spur level (Dual-tone)                        |          | T   |                        |     |        |         |                      |

| 4:1 MUX                                               |          |     |                        |     |        |         |                      |

| Fs = 6.0 GSps @ Fout1 = 2850 MHz,                     | IMDspur  |     | (–69)                  |     | dBm    |         | 4                    |

| Fout2 = 2860 MHz -8 dBFS each tone                    | IMD3spur |     | (–88)                  |     | dBm    |         | 4                    |

| Signal independent Spur (clock-related spur) with 4:1 | MUX      | T   |                        |     |        |         |                      |

| Fc @ 6.0 GSps                                         |          |     | -37                    |     | dBm    |         | 4                    |

| Fc/2 @ 6.0 GSps                                       |          |     | -89                    |     | dBm    |         | 4                    |

| Fc/4 @ 6.0 GSps                                       |          |     | -80                    |     | dBm    |         | 4                    |

| Self-Noise Density at code 0 or 4095 @ 6.0 GSps       |          |     | -149                   |     | dBm/Hz |         | 4                    |

| Noise Power Ratio (1 <sup>st</sup> Nyquist)           |          |     |                        |     |        |         |                      |

| –14 dBFS peak to rms loading factor                   | NPR      |     | 44                     |     | dB     | (4) (5) | 4                    |

| Fs = 6.0 GSps                                         |          |     |                        |     |        |         |                      |

| 2.667 GHz broadband pattern, 33.3 MHz notch width     |          |     |                        |     |        |         |                      |

| Equivalent ENOB (Computed from NPR figure)            | ENOB     |     | 8.8                    |     | Bit    |         | 4                    |

| Signal to Noise Ratio (Computed from NPR figure)      | SNR      |     | 55                     |     | dB     |         | 4                    |

Table 3-5.

AC Electrical Characteristics NRTZ Mode (First & Second Nyquist Zone) (Continued)

| Parameter                                                                                                                                       | Symbol | Min | Тур  | Max | Unit | Notes | Test<br>level <sup>(1)</sup> |

|-------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|------|-----|------|-------|------------------------------|

| Noise Power Ratio (1 <sup>st</sup> Nyquist) -14 dBFS peak to rms loading factor Fs = 3 GSps 1.33 GHz broadband pattern, 17 MHz notch width      | NPR    | 47  | 50   |     | dB   |       | 1                            |

| Equivalent ENOB (Computed from NPR figure)                                                                                                      | ENOB   | 9.3 | 9.8  |     | Bit  |       | 1                            |

| Signal to Noise Ratio (Computed from NPR figure)                                                                                                | SNR    | 58  | 61   |     | dB   |       | 1                            |

| Noise Power Ratio (2 <sup>nd</sup> Nyquist) -14 dBFS peak to rms loading factor Fs = 6.0 GSps 2.667 GHz broadband pattern, 33.3 MHz notch width | NPR    |     | 39.5 |     | dB   |       | 4                            |

| Equivalent ENOB (Computed from NPR figure)                                                                                                      | ENOB   |     | 8.1  |     | Bit  |       | 4                            |

| Signal to Noise Ratio (Computed from NPR figure)                                                                                                | SNR    |     | 50.5 |     | dB   |       | 4                            |

| Noise Power Ratio (2 <sup>nd</sup> Nyquist) -14 dBFS peak to rms loading factor Fs = 3 GSps 1.33 GHz broadband pattern, 17 MHz notch width      | NPR    | 41  | 43.5 |     | dB   |       | 1                            |

| Equivalent ENOB (Computed from NPR figure)                                                                                                      | ENOB   | 8.3 | 8.8  |     | Bit  |       | 1                            |

| Signal to Noise Ratio (Computed from NPR figure)                                                                                                | SNR    | 52  | 54.5 |     | dB   |       | 1                            |

Note: 1. See Section 3.6 on page 18 for explanation of test levels.

- 2. Refer to Figure 7-40 for SFDR variation versus temperature.

- 3. Refer to Figure 7-39 for SFDR variation versus supplies.

- 4. Refer to Figure 7-64 for NPR variation versus temperature.

- 5. Refer to Figure 7-63 for NPR variation versus supplies.

# EV12DS460AZP

**Table 3-6.** AC Electrical Characteristics RTZ Mode (Second Nyquist Zone)

| Parameter                                                                                                                                         | Symbol  | Min  | Тур        | Max | Unit   | Notes   | Test<br>level <sup>(1)</sup> |

|---------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|------------|-----|--------|---------|------------------------------|

| Single-tone Spurious Free Dynamic Range                                                                                                           |         |      |            |     |        |         |                              |

| 4:1 MUX<br>Fs = 6.0 GSps @ Fout = 5940 MHz 0 dBFS<br>Fs = 3.0 GSps @ Fout = 2970 MHz 0 dBFS                                                       | SFDR    | 59   | 56<br>64   |     | dBc    | (2) (3) | 4                            |

| 2:1 MUX<br>Fs = 3.2 GSps @ Fout = 3168 MHz 0 dBFS<br>Fs = 1.5 GSps @ Fout = 1485 MHz 0 dBFS                                                       | SFDR    | 59   | 59<br>66   |     |        | (2) (3) | 4                            |

| Highest spur level                                                                                                                                | 1       |      | 1          |     |        |         |                              |

| 4:1 MUX<br>Fs = 6.0 GSps @ Fout = 5940 MHz 0 dBFS<br>Fs = 3.0 GSps @ Fout = 2970 MHz 0 dBFS                                                       |         |      | -68<br>-74 |     | dBm    |         | 4                            |

| 2:1 MUX<br>Fs = 3.2 GSps @ Fout = 3168 MHz 0 dBFS<br>Fs = 1.5 GSps @ Fout = 1485 MHz 0 dBFS                                                       |         |      | -72<br>-75 |     | dBm    |         | 4                            |

| Signal independent Spur (clock-related spur) with                                                                                                 | 1:1 MUX |      |            |     |        |         |                              |

| Fc @ 6.0 GSps                                                                                                                                     |         |      | -36        |     | dBm    |         | 4                            |

| Fc/2 @ 6.0 GSps                                                                                                                                   |         |      | -87        |     | dBm    |         | 4                            |

| Fc/4 @ 6.0 GSps                                                                                                                                   |         |      | -80        |     | dBm    |         | 4                            |

| Self-Noise Density at code 0 or 4095 @ 6.0 GSps                                                                                                   |         |      | -138       |     | dBm/Hz |         | 4                            |

| Noise Power Ratio (2 <sup>nd</sup> Nyquist)  -14 dBFS peak to rms loading factor Fs = 6.0 GSps  2.667 GHz broadband pattern, 33.3 MHz notch width | NPR     |      | 38         |     | dB     | (4) (5) | 4                            |

| Equivalent ENOB (Computed from NPR figure)                                                                                                        | ENOB    |      | 7.8        |     | Bit    |         | 4                            |

| Signal to Noise Ratio (Computed from NPR figure)                                                                                                  | SNR     |      | 49         |     | dB     |         | 4                            |

| Noise Power Ratio (2 <sup>nd</sup> Nyquist)  -14 dBFS peak to rms loading factor Fs = 3 GSps  1.33 GHz broadband pattern, 17 MHz notch width      | NPR     | 43.5 | 46         |     | dB     |         | 1                            |

| Equivalent ENOB (Computed from NPR figure)                                                                                                        | ENOB    | 8.8  | 9.2        |     | Bit    |         | 1                            |

| Signal to Noise Ratio (Computed from NPR figure)                                                                                                  | SNR     | 54.5 | 57         |     | dB     |         | 1                            |

Note:

- 1. See Section 3.6 on page 18 for explanation of test levels.

- 2. Refer to Figure 7-40 for SFDR variation versus temperature.

- 3. Refer to Figure 7-39 for SFDR variation versus supplies.

- 4. Refer to Figure 7-64 for NPR variation versus temperature.

- 5. Refer to Figure 7-63 for NPR variation versus supplies.

Table 3-7.

AC Electrical Characteristics RF Mode (Second to Eighth Nyquist Zones)

| Parameter                               | Symbol   | Min | Тур                    | Max | Unit | Notes   | Test<br>level <sup>(1)</sup> |

|-----------------------------------------|----------|-----|------------------------|-----|------|---------|------------------------------|

| Single-tone Spurious Free Dynamic Range | <u>.</u> |     |                        |     | •    |         |                              |

| 4:1 MUX                                 |          |     |                        |     |      |         |                              |

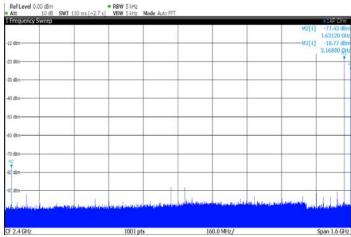

| Fs = 6.0 GSps @ Fout = 5940 MHz 0 dBFS  |          |     | 56 (58)                |     |      |         | 4                            |

| Fs = 6.0 GSps @ Fout = 8940 MHz 0 dBFS  |          |     | 41 (49)                |     |      |         | 4                            |

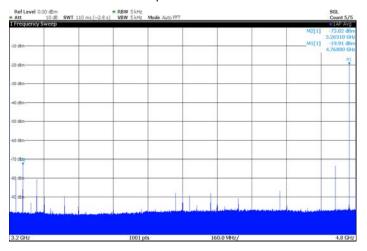

| Fs = 6.0 GSps @ Fout = 11940 MHz 0 dBFS |          |     | 42 (50)                |     |      |         | 4                            |

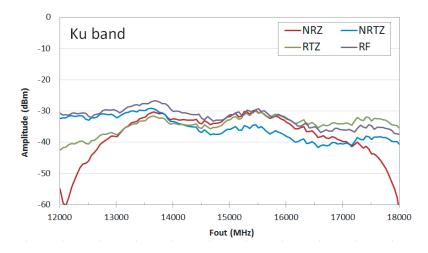

| Fs = 6.0 GSps @ Fout = 17940 MHz 0 dBFS | SFDR     |     | 38 (41)                |     | dBc  | (2) (3) | 4                            |

| Fs = 6.0 GSps @ Fout = 18040 MHz 0 dBFS | Jaruki   |     | 38 (43)                |     | UBC  |         | 4                            |

| Fs = 6.0 GSps @ Fout = 23920 MHz 0 dBFS |          |     | 33 (38)                |     |      |         | 4                            |

| Fs = 3.0 GSps @ Fout = 2970 MHz 0 dBFS  |          | 61  | 65                     |     |      |         | 1                            |

| Fs = 3.0 GSps @ Fout = 4470 MHz 0 dBFS  |          | 49  | 58                     |     |      |         | 1                            |

| 2:1 MUX                                 |          |     |                        |     |      |         |                              |

| Fs = 3.2 GSps @ Fout = 3168 MHz 0 dBFS  |          |     | 58                     |     |      |         | 4                            |

| Fs = 3.2 GSps @ Fout = 4768 MHz 0 dBFS  | Issaal   |     | 54                     |     |      | (2) (3) | 4                            |

|                                         | SFDR     |     |                        |     | dBc  |         |                              |

| Fs = 1.5 GSps @ Fout = 1485 MHz 0 dBFS  |          | 64  | 70                     |     |      |         | 1                            |

| Fs = 1.5 GSps @ Fout = 2235 MHz 0 dBFS  |          | 60  | 65                     |     |      | (6)     | 1                            |

| 4:1 MUX with IUCM2                      |          |     |                        |     |      | (7)     |                              |

| Fs = 6.0 GSps @ Fout = 5940 MHz 0 dBFS  | SFDR     | 54  | 58                     |     | dBc  | (7)     | 1                            |

| Highest spur level (Single tone)        |          |     |                        |     |      |         |                              |

| 4:1 MUX                                 |          |     |                        |     |      |         |                              |

| Fs = 6.0 GSps @ Fout = 6940 MHz 0 dBFS  |          |     | -64 (-73)              |     |      |         | 4                            |

| Fs = 6.0 GSps @ Fout = 8940 MHz 0 dBFS  |          |     | -60 (-69)              |     |      |         | 4                            |

| Fs = 6.0 GSps @ Fout = 11940 MHz 0 dBFS |          |     | -74 (-79)              |     |      |         | 4                            |

| Fs = 6.0 GSps @ Fout = 17940 MHz 0 dBFS |          |     | -76 (-78)              |     | I.D. |         | 4                            |

| Fs = 6.0 GSps @ Fout = 18040 MHz 0 dBFS |          |     | -77 ( <del>-</del> 82) |     | dBm  |         | 4                            |

| Fs = 6.0 GSps @ Fout = 23920 MHz 0 dBFS |          |     | -79 (-77)              |     |      |         | 4                            |

| Fs = 3.0 GSps @ Fout = 2970 MHz 0 dBFS  |          |     | -69                    |     |      |         | 1                            |

| Fs = 3.0 GSps @ Fout = 4470 MHz 0 dBFS  |          |     | -67                    |     |      |         | 1                            |

| 2:1 MUX                                 |          |     |                        |     |      |         |                              |

| Fs = 3.2 GSps @ Fout = 1568 MHz 0 dBFS  |          |     | <b>-</b> 65            |     |      |         | 4                            |

| Fs = 3.2 GSps @ Fout = 4768 MHz 0 dBFS  |          |     | -66                    |     | dBm  |         | 4                            |

| Fs = 1.5 GSps @ Fout = 1485 MHz 0 dBFS  |          |     | <b>-73</b>             |     |      |         | 1                            |

| Fs = 1.5 GSps @ Fout = 2235 MHz 0 dBFS  |          |     | <b>-7</b> 5            |     |      |         | 1                            |

| 4:1 MUX with IUCM2                      |          |     | _6.4                   |     | dPm  | (7)     | 1                            |

| Fs = 6.0 GSps @ Fout = 5940 MHz 0 dBFS  |          |     | -64                    |     | dBm  | V-7     | 1                            |

# EV12DS460AZP

Table 3-7.

AC Electrical Characteristics RF Mode (Second to Eighth Nyquist Zones) (Continued)

| Parameter                                                               | Symbol     | Min | Тур             | Max | Unit       | Notes   | Test<br>level <sup>(1)</sup> |

|-------------------------------------------------------------------------|------------|-----|-----------------|-----|------------|---------|------------------------------|

| Signal independent Spur (clock-related spur) with                       | 4:1 MUX    |     |                 |     |            |         |                              |

| Fc @ 6.0 GSps                                                           |            |     | <del>-</del> 37 |     | dBm        |         | 4                            |

| Fc/2 @ 6.0 GSps                                                         |            |     | -87             |     | dBm        |         | 4                            |

| Fc/4 @ 6.0 GSps                                                         |            |     | -85             |     | dBm        |         | 4                            |

| Dual-tone over Full Nyquist                                             |            |     |                 |     |            |         | 1                            |

| 4:1 MUX                                                                 |            |     |                 |     |            |         |                              |

| Fs = 6.0 GSps @ Fout1 = 2850 MHz,                                       | IMD        |     | (54)            |     |            |         | 4                            |

| Fout2 = 2860 MHz -8 dBFS each tone                                      | IMD3       |     | (73)            |     |            |         | 4                            |

| Fs = 6.0 GSps @ Fout1 = 5750 MHz,                                       | IMD        |     | (53)            |     |            |         | 4                            |

| Fout2 = 5760 MHz -8 dBFS each tone                                      | IMD3       |     | (64)            |     |            |         | 4                            |

|                                                                         |            |     | ,               |     | dBc        |         |                              |

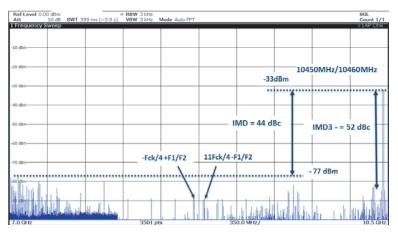

| Fs = 6.0 GSps @ Fout1 = 8850 MHz,                                       | IMD        |     | (44)            |     |            |         | 4                            |

| Fout2 = 8860 MHz -8 dBFS each tone                                      | IMD3       |     | (57)            |     |            |         | 4                            |

|                                                                         |            |     | (- /            |     |            |         |                              |

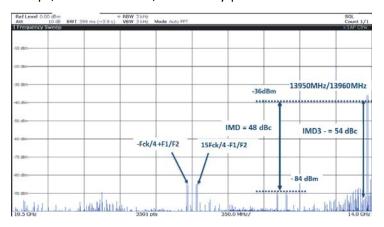

| Fs = 6.0 GSps @ Fout1 = 11850 MHz,                                      | IMD        |     | (41)            |     |            |         | 4                            |

| Fout2 = 11860 MHz -8 dBFS each tone                                     | IMD3       |     | (58)            |     |            |         | 4                            |

| Highest spur level (Dual-tone)                                          |            |     | ,               |     |            |         |                              |

| 4:1 MUX                                                                 |            |     |                 |     |            |         |                              |

| Fs = 6.0 GSps @ Fout1 = 2850 MHz,                                       | IMDspur    |     | (-69)           |     |            |         | 4                            |

| Fout2 = 2860 MHz -8 dBFS each tone                                      | IMD3spur   |     | (-88)           |     |            |         | 4                            |

| 5 6065 05 14 575014                                                     | IMDspur    |     | (-73)           |     |            |         | 4                            |

| Fs = 6.0 GSps @ Fout1 = 5750 MHz,<br>Fout2 = 5760 MHz -8 dBFS each tone | IMD3spur   |     |                 |     |            |         | 4                            |

| FOULZ = 3760 IVITIZ -8 UBF3 Each tone                                   | liviD3spur |     | (–84)           |     | dBm        |         | 4                            |

| Fs = 6.0 GSps @ Fout1 = 8850 MHz,                                       | IMDspur    |     | (-73)           |     |            |         | 4                            |

| Fout2 = 8860 MHz -8 dBFS each tone                                      | IMD3spur   |     | (–86)           |     |            |         | 4                            |

|                                                                         |            |     |                 |     |            |         |                              |

| Fs = 6.0 GSps @ Fout1 = 11850 MHz,                                      | IMDspur    |     | (-75)           |     |            |         | 4                            |

| Fout2 = 11860 MHz –8 dBFS each tone                                     | IMD3spur   |     | (-92)           |     |            |         | 4                            |

| Self-Noise Density at code 0 or 4095 @ 6.0 GSps                         |            |     | -135            |     | dBm/<br>Hz |         | 4                            |

| Noise Power Ratio (2 <sup>nd</sup> Nyquist)                             |            |     |                 |     |            |         |                              |

| -14 dBFS peak to rms loading factor                                     |            |     |                 |     |            |         |                              |

| Fs = 6.0 GSps                                                           | NPR        |     | 37.5            |     | dB         | (4) (5) | 4                            |

| 2.667 GHz broadband pattern, 33.3 MHz notch width                       |            |     |                 |     |            |         |                              |

| Equivalent ENOB (Computed from NPR figure)                              | ENOB       |     | 7.8             |     | Bit        |         | 4                            |

| Signal to Noise Ratio (Computed from NPR figure)                        | SNR        |     | 48.5            |     | dB         |         | 4                            |

Table 3-7. AC Electrical Characteristics RF Mode (Second to Eighth Nyquist Zones) (Continued)

| Parameter                                                                                                                                         | Symbol | Min  | Тур  | Max | Unit | Notes | Test<br>level <sup>(1)</sup> |

|---------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|------|-----|------|-------|------------------------------|

| Noise Power Ratio (2 <sup>nd</sup> Nyquist)  -14 dBFS peak to rms loading factor Fs = 3 GSps  1.33 GHz broadband pattern, 17 MHz notch width      | NPR    | 42.5 | 45   |     | dB   |       | 1                            |

| Equivalent ENOB (Computed from NPR figure)                                                                                                        | ENOB   | 8.6  | 9.0  |     | Bit  |       | 1                            |

| Signal to Noise Ratio (Computed from NPR figure)                                                                                                  | SNR    | 53.5 | 56   |     | dB   |       | 1                            |

| Noise Power Ratio (3 <sup>rd</sup> Nyquist)  -14 dBFS peak to rms loading factor Fs = 6.0 GSps  2.667 GHz broadband pattern, 33.3 MHz notch width | NPR    |      | 36.5 |     | dB   |       | 4                            |

| Equivalent ENOB (Computed from NPR figure)                                                                                                        | ENOB   |      | 7.6  |     | Bit  |       | 4                            |

| Signal to Noise Ratio (Computed from NPR figure)                                                                                                  | SNR    |      | 47.5 |     | dB   |       | 4                            |

| Noise Power Ratio (3 <sup>rd</sup> Nyquist)  -14 dBFS peak to rms loading factor Fs = 3 GSps  1.33 GHz broadband pattern, 17 MHz notch width      | NPR    | 39   | 42   |     | dB   |       | 1                            |

| Equivalent ENOB (Computed from NPR figure)                                                                                                        | ENOB   | 8.0  | 8.5  |     | Bit  |       | 1                            |

| Signal to Noise Ratio (Computed from NPR figure)                                                                                                  | SNR    | 50   | 53   |     | dB   |       | 1                            |

Notes: 1. See Section 3.6 on page 18 for explanation of test levels.

- 2. Refer to Figure 7-40 for SFDR variation versus temperature.

- 3. Refer to Figure 7-39 for SFDR variation versus supplies.

- 4. Refer to Figure 7-64 for NPR variation versus temperature.

- 5. Refer to Figure 7-63 for NPR variation versus supplies.

- 6. This measurement at Fs = 1.5 GSps is done with RPB1 and RPW1.

- 7. The corresponding spectrum shows an output frequency at 5940 MHz within an 1500 MHz wide Nyquist zone.

# 3.5 Timing Characteristics and Switching Performances

Unless otherwise specified:  $V_{CCA5} = 5V$ ,  $V_{CCA3} = 3.3V$ ,  $V_{CCD} = 3.3V$ , 4:1 MUX ratio, room temperature, typical swing on input data, typical Pclk, Master clock input jitter is below 100 fs rms integrated over 11 GHz bandwidth.

**Table 3-8.** Timing characteristics and Switching Performances

| Parameter                             | Symbol | Value | Unit | Note | Test Level <sup>(1)</sup> |

|---------------------------------------|--------|-------|------|------|---------------------------|

| SWITCHING PERFORMANCE AND CHARACTERIS |        |       |      |      |                           |

| Maximum operating clock frequency     |        |       |      |      |                           |

| 4:1 MUX mode                          |        | 6.0   | GHz  |      | 4                         |

| 2:1 MUX mode                          |        | 3.2   | GHz  |      | 4                         |

| Minimum operating clock frequency     |        | 300   | MHz  | (2)  | 5                         |

| Parameter                                                   | Symbol             | Min | Тур                                     | Max  | Unit   | Note | Test Level <sup>(1)</sup> |

|-------------------------------------------------------------|--------------------|-----|-----------------------------------------|------|--------|------|---------------------------|

| TIMING CHARACTERISTICS                                      | <u>'</u>           |     |                                         |      |        |      |                           |

| Input Data timing                                           |                    |     |                                         |      |        |      |                           |

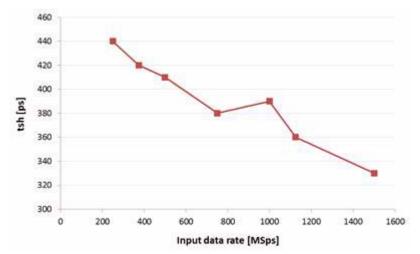

| Input data setup and hold time                              | t <sub>SH</sub>    |     | 360                                     |      | ps     | (3)  | 4                         |

| Input data rate (4:1 MUX)                                   |                    |     |                                         | 1500 | Msps   |      | 4                         |

| Input data rate (2:1 MUX)                                   |                    |     |                                         | 1600 | Msps   |      | 4                         |

| Data clock output timing (DSP, DSPN)                        |                    |     |                                         |      |        |      |                           |

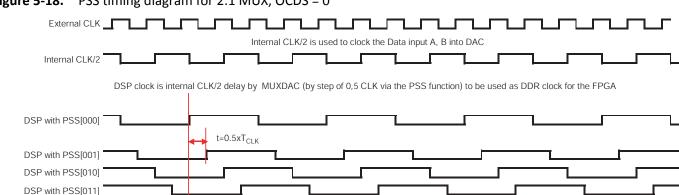

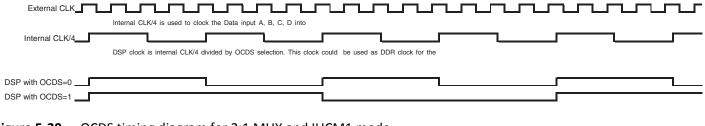

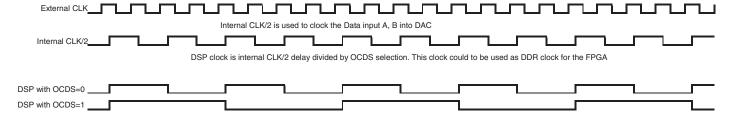

| DSP clock phase tuning steps                                | PSS                |     | 0.5                                     |      | Tclock |      | 5                         |

| Master clock to DSP timing                                  |                    |     |                                         |      |        |      |                           |

| Pipeline (4:1 MUX)                                          |                    |     | 3                                       |      | Talaal | (4)  | 5                         |

| Pipeline (2:1 MUX)                                          |                    |     | 3                                       |      | Tclock |      | 5                         |

| Delay 4:1 MUX                                               |                    |     | 540                                     |      |        |      | 4                         |

| Delay 2:1 MUX                                               | t <sub>PD</sub>    |     | 540                                     |      | ps     |      | 4                         |

| SYNC to DSP, DSPN                                           | •                  |     |                                         |      |        |      |                           |

| Sync falling edge to DSP rising edge<br>Pipeline in 4:1 MUX |                    |     | 3                                       |      | Tclock |      | 5                         |

| Sync falling edge to DSP rising edge<br>Pipeline in 2:1 MUX |                    |     | 3                                       |      | Tclock |      | 5                         |

| Sync falling edge to DSP rising edge                        |                    |     |                                         |      |        | (5)  |                           |

| Delay with 2:1 MUX                                          |                    |     | 640                                     |      | ps     |      | 4                         |

| Delay with 4:1 MUX                                          | t <sub>SDSP</sub>  |     | 640                                     |      | ps     |      | 4                         |

| Sync rising edge to DSP falling edge                        | t <sub>SDSPF</sub> |     | T <sub>CLK</sub> + 1/2 T <sub>DSP</sub> |      | ps     |      | 5                         |

| Parameter                        | Symbol           | Min | Тур                              | Max | Unit   | Note | Test Level <sup>(1)</sup> |

|----------------------------------|------------------|-----|----------------------------------|-----|--------|------|---------------------------|

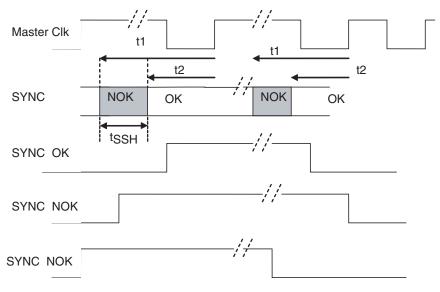

| SYNC timing                      |                  |     |                                  |     |        |      |                           |

| Minimum Sync pulse width         |                  |     | 3                                |     | Tclock |      | 4                         |

| SYNC setup and hold time         | t <sub>ssh</sub> |     | 15                               |     | ps     |      | 4                         |

| SYNC forbidden area lower bound  | t <sub>1</sub>   |     | 100                              |     | ps     | (6)  | 4                         |

| SYNC forbidden area upper bound  | t <sub>2</sub>   |     | t <sub>1</sub> -t <sub>SSH</sub> |     | ps     |      | 4                         |

| Analog output timing             |                  |     |                                  |     |        | •    |                           |

| Analog output rise time (20-80%) | t <sub>OR</sub>  |     | 30                               |     | ps     |      | 4                         |

| Analog output fall time (20-80%) | t <sub>OF</sub>  |     | 30                               |     | ps     |      | 4                         |

| Pipeline (4:1 MUX)               |                  |     | 3                                |     |        | (4)  | 5                         |

| Pipeline (2:1 MUX)               |                  |     | 3                                |     | Tclock | (4)  | 5                         |

| Analog output delay              | t <sub>op</sub>  |     | 560                              |     | ps     | (4)  | 4                         |

Notes: 1. See Section 3.6 on page 18 for explanation of test levels.

- 2. Minimum operating clock frequency can be DC. It depends on the clock input AC coupling capacitor used in the final application and limitation due to the environment as circuit itself displays no lower clock frequency limitation.

- 3. Set up and hold time were measured on Teledyne e2v evaluation board and as such include the impact from FPGA (jitter and skew) and PCB skew on the board. Refer to Figure 7-66 on Section 7.3 on page 78. t<sub>SH</sub> variation over temperature range is around 20 ps.

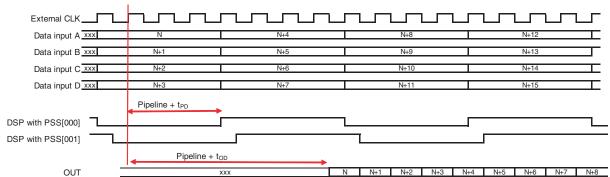

- 4. See Figure 3-1 and Figure 3-2 below.

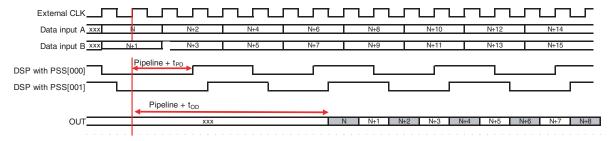

- 5. See Figure 3-3 below.

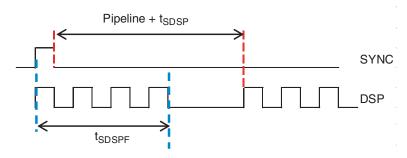

- 6. See Figure 3-4 below.

Figure 3-1. Timing Diagram for 4:1 MUX principle of operation OCDS1, IUCM1

Figure 3-2. Timing Diagram for 2:1 MUX principle of operation OCDS1, IUCM1

Figure 3-3. Timing relationship between SYNC and DSP

Figure 3-4. SYNC Timing Diagram

# 3.6 Explanation of Test Levels

Table 3-9. Test levels

| 1 | 100% production tested at +25°C <sup>(1)</sup>                                                                  |

|---|-----------------------------------------------------------------------------------------------------------------|

| 2 | 100% production tested at +25°C <sup>(1)</sup> , and sample tested at specified temperatures.                   |

| 3 | Sample tested only at specified temperatures                                                                    |

| 4 | Parameter is guaranteed by characterization testing (thermal steady-state conditions at specified temperature). |

| 5 | Parameter value is only guaranteed by design                                                                    |

Only MIN and MAX values are guaranteed.

Note: 1. Unless otherwise specified.

# 3.7 Digital Input Coding Table

Table 3-10.

Coding Table (Theorical values)

| Digital output<br>msblsb | Differential analog output |

|--------------------------|----------------------------|

| 0000000000               | –500 mV                    |

| 01000000000              | −250 mV                    |

| 01100000000              | −125 mV                    |

| 01111111111              | −0.122 mV                  |

| 10000000000              | 0.122 mV                   |

| 10100000000              | +125 mV                    |

| 11000000000              | +250 mV                    |

| 1111111111               | +500 mV                    |

# 4. DEFINITION OF TERMS

**Table 4-1.** Definition of Terms

| Abbreviation | Term                         | Definition                                                                                                                                                                                                                                                                                                                                                            |

|--------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (SFDR)       | Spurious free dynamic range  | Ratio expressed in dBC of the signal power, set at Full Scale, to the power of the highest spurious spectral component over the Nyquist zone. The peak spurious component may or may not be a harmonic.                                                                                                                                                               |

| (HSL)        | Highest Spur Level           | Power of the highest spurious spectral component expressed in dBm.                                                                                                                                                                                                                                                                                                    |

| (ENOB)       | Effective Number Of Bits     | ENOB is calculated from NPR measurement using the formula: $  ENOB = (NPR_{[dB]} +  LF_{[dB]}  - 3 - 1.76) / 6.02 $ Where LF is the loading factor i.e. the ratio between the Gaussian noise standard deviation versus amplitude full scale of the NPR pattern.                                                                                                       |

| (SNR)        | Signal to noise ratio        | SNR is calculated from NPR measurement using the formula:                                                                                                                                                                                                                                                                                                             |

| (NPR)        | Noise Power Ratio            | The NPR is measured to characterize the DAC performance in response to broad band signals. When applying a notch-filtered broadband white-noise pattern at the input of the DAC under test, the Noise Power Ratio is defined as the ratio between the average noise measured on the shoulder of the notch and inside the notch, using the same integration bandwidth. |

| (DNL)        | Differential non linearity   | The Differential Non Linearity for a given code i is the difference between the measured step size of code i and the ideal LSB step size. DNL (i) is expressed in LSBs. DNL is the maximum value of all DNL (i). DNL error specification of less than 1 LSB guarantees that there is no missing point and that the transfer function is monotonic.                    |

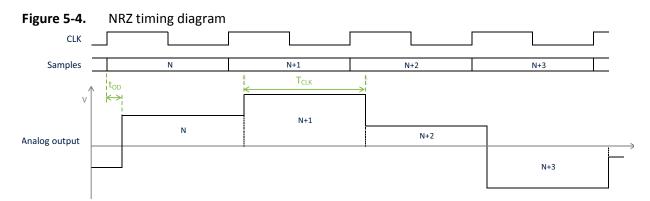

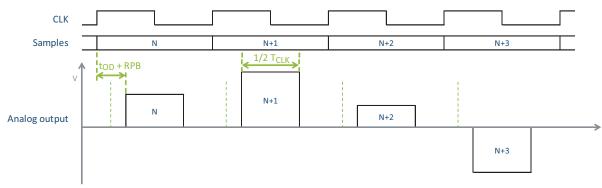

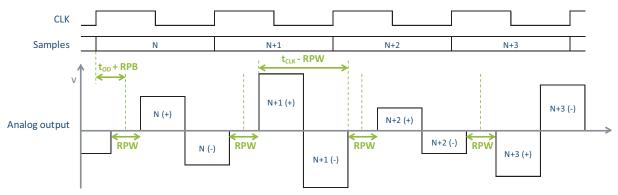

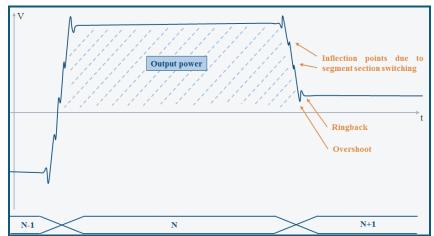

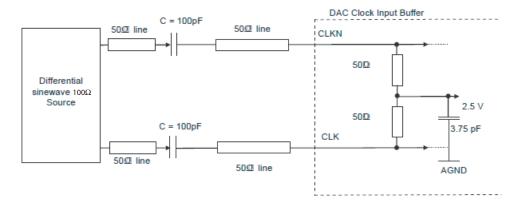

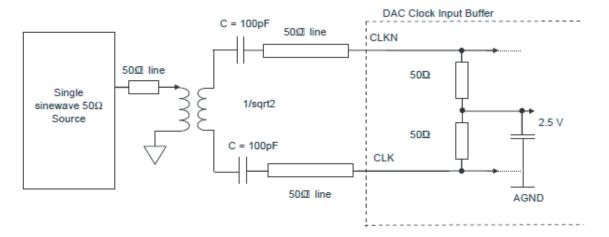

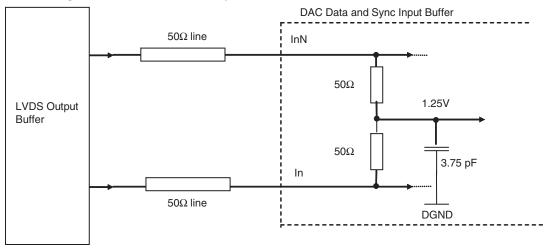

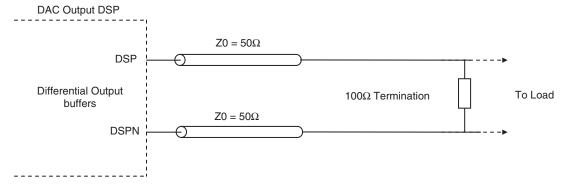

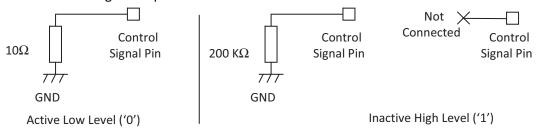

| (INL)        | Integral non linearity       | The Integral Non Linearity for a given code i is the difference between the measured voltage at which the transition occurs and the ideal value of this transition.  INL (i) is expressed in LSBs, and is the maximum value of all  INL (i) .                                                                                                                         |